#### 2015.05.08

## A10-DATASHEET Subscribe Send Feedback

This datasheet describes the electrical characteristics, switching characteristics, configuration specifications, and I/O timing for Arria<sup>®</sup> 10 devices.

Arria 10 devices are offered in extended and industrial grades. Extended devices are offered in -E1 (fastest), -E2, and -E3 speed grades. Industrial grade devices are offered in the -I1, -I2, and -I3 speed grades.

The suffix after the speed grade denotes the power options offered in Arria 10 devices.

- L—Low static power

- S—Standard power

- M—Enabled with the  $V_{CC}$  PowerManager feature (you can power  $V_{CC}$  and  $V_{CCP}$  at nominal voltage of 0.90 V or lower voltage of 0.83 V)

#### **Related Information**

#### Arria 10 Device Overview

Provides more information about the densities and packages of devices in the Arria 10 family.

# **Electrical Characteristics**

The following sections describe the operating conditions and power consumption of Arria 10 devices.

# **Operating Conditions**

Arria 10 devices are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of the Arria 10 devices, you must consider the operating requirements described in this section.

© 2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

## **Absolute Maximum Ratings**

This section defines the maximum operating conditions for Arria 10 devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied for these conditions.

**Caution:** Conditions outside the range listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

#### Table 1: Absolute Maximum Ratings for Arria 10 Devices—Preliminary

| Symbol                   | Description                                                            | Condition | Minimum | Maximum | Unit |

|--------------------------|------------------------------------------------------------------------|-----------|---------|---------|------|

| V <sub>CC</sub>          | Core voltage power supply                                              | _         | -0.50   | 1.21    | V    |

| V <sub>CCP</sub>         | Periphery circuitry and transceiver fabric interface power supply      | _         | -0.50   | 1.21    | V    |

| V <sub>CCERAM</sub>      | Embedded memory power supply                                           | _         | -0.50   | 1.36    | V    |

| V <sub>CCPT</sub>        | Power supply for programmable power technology and I/O pre-driver      |           | -0.50   | 2.46    | V    |

| V <sub>CCBAT</sub>       | Battery back-up power supply for design security volatile key register | _         | -0.50   | 2.46    | V    |

| V <sub>CCPGM</sub>       | Configuration pins power supply                                        | _         | -0.50   | 2.46    | V    |

| V                        | I/O huffore new or supply                                              | 3 V I/O   | -0.50   | 4.10    | V    |

| V <sub>CCIO</sub>        | I/O buffers power supply                                               | LVDS I/O  | -0.50   | 2.46    | V    |

| V <sub>CCA_PLL</sub>     | Phase-locked loop (PLL) analog power supply                            | _         | -0.50   | 2.46    | V    |

| V <sub>CCT_GXB</sub>     | Transmitter power                                                      | _         | -0.50   | 1.34    | V    |

| V <sub>CCR_GXB</sub>     | Receiver power                                                         |           | -0.50   | 1.34    | V    |

| V <sub>CCH_GXB</sub>     | Transmitter output buffer power                                        | _         | -0.50   | 2.46    | V    |

| V <sub>CCL_HPS</sub>     | HPS core voltage and periphery circuitry power supply                  | _         | -0.50   | 1.27    | V    |

| V                        | HDS I/O buffare power supply                                           | 3 V I/O   | -0.50   | 4.10    | V    |

| V <sub>CCIO_HPS</sub>    | HPS I/O buffers power supply                                           | LVDS I/O  | -0.50   | 2.46    | V    |

| V <sub>CCIOREF_HPS</sub> | HPS I/O pre-driver power supply                                        | _         | -0.50   | 2.46    | V    |

| Symbol                 | Description                    | Condition | Minimum | Maximum | Unit |

|------------------------|--------------------------------|-----------|---------|---------|------|

| V <sub>CCPLL_HPS</sub> | HPS PLL power supply           | _         | -0.50   | 2.46    | V    |

| I <sub>OUT</sub>       | DC output current per pin      |           | -25     | 25      | mA   |

| T <sub>J</sub>         | Operating junction temperature |           | -55     | 125     | °C   |

| T <sub>STG</sub>       | Storage temperature (no bias)  |           | -65     | 150     | °C   |

#### Maximum Allowed Overshoot and Undershoot Voltage

During transitions, input signals may overshoot to the voltage listed in the following table and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% duty cycle.

For example, a signal that overshoots to 2.70 V for LVDS I/O can only be at 2.70 V for ~4% over the lifetime of the device.

#### Table 2: Maximum Allowed Overshoot During Transitions for Arria 10 Devices—Preliminary

This table lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime. The LVDS I/O values are applicable to the VREFP\_ADC and VREFN\_ADC I/O pins.

| Symbol  | Description      | Condit       | ion (V)      | Overshoot Duration as % at $T_J = 100^{\circ}C$ | Unit |

|---------|------------------|--------------|--------------|-------------------------------------------------|------|

| Symbol  | Description      | LVDS I/O     | 3 V I/O      |                                                 | Ont  |

|         |                  | 2.50         | 3.80         | 100                                             | %    |

|         |                  | 2.55         | 2.55 3.85 42 |                                                 | %    |

| Vi (AC) | AC input voltage | 2.60 3.90 18 |              | %                                               |      |

| VI (AC) | AC input voltage | 2.65 3.95 9  |              | 9                                               | %    |

|         |                  | 2.70 4.00 4  |              | %                                               |      |

|         |                  | > 2.70       | > 4.00       | No overshoot allowed                            | %    |

## **Recommended Operating Conditions**

This section lists the functional operation limits for the AC and DC parameters for Arria 10 devices.

4

### **Recommended Operating Conditions**

## Table 3: Recommended Operating Conditions for Arria 10 Devices—Preliminary

This table lists the steady-state voltage values expected from Arria 10 devices. Power supply ramps must all be strictly monotonic, without plateaus.

| Symbol                            | Description                                                       | Condition                                   | Minimum <sup>(1)</sup> | Typical   | Maximum <sup>(1)</sup> | Unit |

|-----------------------------------|-------------------------------------------------------------------|---------------------------------------------|------------------------|-----------|------------------------|------|

|                                   |                                                                   | Standard and low power                      | 0.87                   | 0.9 (2)   | 0.93                   | V    |

| V <sub>CC</sub>                   | Core voltage power supply                                         | V <sub>CC</sub> PowerManager <sup>(3)</sup> | 0.8, 0.87              | 0.83, 0.9 | 0.86, 0.93             | V    |

|                                   |                                                                   | SmartVID                                    | 0.8                    |           | 0.93                   | V    |

|                                   |                                                                   | Standard and low power                      | 0.87                   | 0.9 (2)   | 0.93                   | V    |

| V <sub>CCP</sub>                  | Periphery circuitry and transceiver fabric interface power supply | V <sub>CC</sub> PowerManager <sup>(3)</sup> | 0.8, 0.87              | 0.83, 0.9 | 0.86, 0.93             | V    |

|                                   | 1 11 /                                                            | SmartVID                                    | 0.8                    | _         | 0.93                   | V    |

|                                   |                                                                   | 1.8 V                                       | 1.71                   | 1.8       | 1.89                   | V    |

| V <sub>CCPGM</sub>                | Configuration pins power supply                                   | 1.5 V                                       | 1.425                  | 1.5       | 1.575                  | V    |

|                                   |                                                                   | 1.2 V                                       | 1.14                   | 1.2       | 1.26                   | V    |

| V <sub>CCERAM</sub>               | Embedded memory power supply                                      | 0.9 V                                       | 0.87                   | 0.9(2)    | 0.93                   | V    |

| <b>V</b> (4)                      | Battery back-up power supply                                      | 1.8 V                                       | 1.71                   | 1.8       | 1.89                   | V    |

| V <sub>CCBAT</sub> <sup>(4)</sup> | (For design security volatile key register)                       | 1.2 V                                       | 1.14                   | 1.2       | 1.26                   | V    |

<sup>&</sup>lt;sup>(1)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(2)</sup> You can operate -1 and -2 speed grade devices at 0.9 V or 0.95 V typical value. You can operate -3 speed grade device at only 0.9 V typical value. Core performance shown in this datasheet is applicable for the operation at 0.9 V. Operating at 0.95 V results in higher core performance and higher power consumption. For more information about the performance and power consumption of 0.95 V operation, refer to the Quartus<sup>®</sup> II software timing reports, PowerPlay Power Analyzer report, and Early Power Estimator (EPE).

<sup>&</sup>lt;sup>(3)</sup> You can operate V<sub>CC</sub> PowerManager devices at either 0.83 V or 0.9 V. Power V<sub>CC</sub> and V<sub>CCP</sub> at 0.9 V to achieve –1 speed grade performance. Power V<sub>CC</sub> and V<sub>CCP</sub> at 0.83 V to achieve lower performance using the lowest power.

<sup>&</sup>lt;sup>(4)</sup> If you do not use the design security feature in Arria 10 devices, connect V<sub>CCBAT</sub> to a 1.5-V or 1.8-V power supply. Arria 10 power-on reset (POR) circuitry monitors V<sub>CCBAT</sub>. Arria 10 devices do not exit POR if V<sub>CCBAT</sub> is not powered up.

A10-DATASHEET 2015.05.08

| Symbol                              | Description                                                       | Condition                | Minimum <sup>(1)</sup> | Typical | Maximum <sup>(1)</sup> | Unit |

|-------------------------------------|-------------------------------------------------------------------|--------------------------|------------------------|---------|------------------------|------|

| V <sub>CCPT</sub>                   | Power supply for programmable power technology and I/O pre-driver | 1.8 V                    | 1.71                   | 1.8     | 1.89                   | V    |

|                                     |                                                                   | 3.0 V (for 3 V I/O only) | 2.85                   | 3.0     | 3.15                   | V    |

|                                     |                                                                   | 2.5 V (for 3 V I/O only) | 2.375                  | 2.5     | 2.625                  | V    |

|                                     |                                                                   | 1.8 V                    | 1.71                   | 1.8     | 1.89                   | V    |

| V <sub>CCIO</sub>                   | I/O buffers power supply                                          | 1.5 V                    | 1.425                  | 1.5     | 1.575                  | V    |

|                                     |                                                                   | 1.35 V                   | (5)                    | 1.35    | (5)                    | V    |

|                                     |                                                                   | 1.25 V                   | 1.19                   | 1.25    | 1.31                   | V    |

|                                     |                                                                   | 1.2 V                    | (5)                    | 1.2     | (5)                    | V    |

| V <sub>CCA_PLL</sub>                | PLL analog voltage regulator power supply                         | _                        | 1.71                   | 1.8     | 1.89                   | V    |

| V <sub>REFP_ADC</sub>               | Precision voltage reference for voltage sensor                    | _                        | 1.2475                 | 1.25    | 1.2525                 | V    |

| V                                   | DC input voltage                                                  | 3 V I/O                  | -0.3                   | _       | 3.3                    | V    |

| VI                                  | DC input voltage                                                  | LVDS I/O                 | -0.3                   | _       | 2.19                   | V    |

| V <sub>O</sub>                      | Output voltage                                                    |                          | 0                      | _       | V <sub>CCIO</sub>      | V    |

| т                                   | Operating is action temperature                                   | Extended                 | 0                      | _       | 100                    | °C   |

| TJ                                  | Operating junction temperature                                    | Industrial               | -40                    |         | 100                    | °C   |

| <b>t</b> (6)(7)                     | Design complements time                                           | Standard POR             | 200 µs                 | _       | 100 ms                 | _    |

| t <sub>RAMP</sub> <sup>(6)(7)</sup> | Power supply ramp time                                            | Fast POR                 | 200 µs                 | _       | 4 ms                   | _    |

<sup>(1)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(5)</sup> For minimum and maximum voltage values, refer to the I/O Standard Specifications section.

$^{(7)}$  t<sub>ramp</sub> is the ramp time of each individual power supply, not the ramp time of all combined power supplies.

<sup>&</sup>lt;sup>(6)</sup> This is also applicable to HPS power supply. For HPS power supply, refer to  $t_{RAMP}$  specifications for standard POR when HPS\_PORSEL = 0 and  $t_{RAMP}$  specifications for fast POR when HPS\_PORSEL = 1.

Transceiver Power Supply Operating Conditions

#### **Related Information**

6

I/O Standard Specifications on page 15

**Transceiver Power Supply Operating Conditions**

#### Table 4: Transceiver Power Supply Operating Conditions for Arria 10 GX/SX Devices—Preliminary

| Symbol                    | Description                    | Condition <sup>(8)</sup>             | Minimum <sup>(9)</sup> | Typical | Maximum <sup>(9)</sup> | Unit |

|---------------------------|--------------------------------|--------------------------------------|------------------------|---------|------------------------|------|

|                           |                                | Chip-to-Chip ≤ 17.4 Gbps             | 1.0                    | 1.03    | 1.06                   | V    |

|                           |                                | Or                                   |                        |         |                        |      |

| V                         | Transmitter power supply       | Backplane $^{(10)} \leq 16.0$ Gbps   |                        |         |                        |      |

| V <sub>CCT_GXB[L,R]</sub> | Transmitter power suppry       | Chip-to-Chip ≤ 11.3 Gbps             | 0.870                  | 0.9     | 0.930                  | V    |

|                           |                                | Or                                   |                        |         |                        |      |

|                           |                                | Backplane $^{(10)} \le 10.3125$ Gbps |                        |         |                        |      |

|                           |                                | Chip-to-Chip ≤ 17.4 Gbps             | 1.0                    | 1.03    | 1.06                   | V    |

|                           |                                | Or                                   |                        |         |                        |      |

| V                         | Desition of the second second  | Backplane $^{(10)} \leq 16.0$ Gbps   |                        |         |                        |      |

| V <sub>CCR_GXB[L,R]</sub> | Receiver power supply          | Chip-to-Chip ≤ 11.3 Gbps             | 0.870                  | 0.9     | 0.930                  | V    |

|                           |                                | Or                                   |                        |         |                        |      |

|                           |                                | Backplane $^{(10)} \le 10.3125$ Gbps |                        |         |                        |      |

| V <sub>CCH_GXB[L,R]</sub> | Transceiver high voltage power | _                                    | 1.710                  | 1.8     | 1.890                  | V    |

<sup>&</sup>lt;sup>(8)</sup> These data rate ranges vary depending on the transceiver speed grade. Refer to Transceiver Performance for Arria 10 GX/SX Devices for exact data rate ranges.

<sup>&</sup>lt;sup>(9)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(10)</sup> Backplane applications assume advanced equalization circuitry, such as decision feedback equalization (DFE), is enabled to compensate for signal impairments. Chip-to-chip links are assumed to be applications with short reach channels that do not require DFE.

**Note:** Most VCCR\_GXB and VCCT\_GXB pins associated with unused transceiver channels can be grounded on a per-side basis to minimize power consumption. Refer to the Quartus II pin report for information about pinning out the package to minimize power consumption for your specific design.

#### Table 5: Transceiver Power Supply Operating Conditions for Arria 10 GT Devices—Preliminary

| Symbol                    | Description              | Condition <sup>(11)</sup>                | Minimum <sup>(9)</sup> | Typical | Maximum <sup>(9)</sup> | Unit |

|---------------------------|--------------------------|------------------------------------------|------------------------|---------|------------------------|------|

|                           |                          | Chip-to-Chip < 28.3 Gbps <sup>(12)</sup> | 1.08                   | 1.11    | 1.14                   | V    |

|                           |                          | Or                                       |                        |         |                        |      |

|                           |                          | Backplane <sup>(10)</sup> < 17.4 Gbps    |                        |         |                        |      |

|                           |                          | Chip-to-Chip < 15 Gbps                   | 1.0                    | 1.03    | 1.06                   | V    |

| V <sub>CCT_GXB[L,R]</sub> | Transmitter power supply | Or                                       |                        |         |                        |      |

|                           |                          | Backplane <sup>(10)</sup> < 14.2 Gbps    |                        |         |                        |      |

|                           |                          | Chip-to-Chip < 11.3 Gbps                 | 0.870                  | 0.9     | 0.930                  | V    |

|                           |                          | Or                                       |                        |         |                        |      |

|                           |                          | Backplane <sup>(10)</sup> < 10.3125 Gbps |                        |         |                        |      |

<sup>&</sup>lt;sup>(11)</sup> These data rate ranges vary depending on the transceiver speed grade. Refer to Transceiver Performance for Arria 10 GT Devices table for exact data rate ranges.

<sup>&</sup>lt;sup>(12)</sup> 28.3 Gbps is the maximum data rate for GT channels. 17.4 Gbps is the maximum data rate for GX channels.

| Symbol                    | Description                           | Condition <sup>(11)</sup>                | Minimum <sup>(9)</sup> | Typical | Maximum <sup>(9)</sup> | Unit |

|---------------------------|---------------------------------------|------------------------------------------|------------------------|---------|------------------------|------|

|                           |                                       | Chip-to-Chip < 28.3 Gbps <sup>(12)</sup> | 1.08                   | 1.11    | 1.14                   | V    |

|                           |                                       | Or                                       |                        |         |                        |      |

|                           |                                       | Backplane <sup>(10)</sup> < 17.4 Gbps    |                        |         |                        |      |

|                           |                                       | Chip-to-Chip < 15 Gbps                   | 1.0                    | 1.03    | 1.06                   | V    |

| V <sub>CCR_GXB[L,R]</sub> | Receiver power supply                 | Or                                       |                        |         |                        |      |

|                           |                                       | Backplane <sup>(10)</sup> < 14.2 Gbps    |                        |         |                        |      |

|                           |                                       | Chip-to-Chip < 11.3 Gbps                 | 0.870                  | 0.9     | 0.930                  | V    |

|                           |                                       | Or                                       |                        |         |                        |      |

|                           |                                       | Backplane <sup>(10)</sup> < 10.3125 Gbps |                        |         |                        |      |

| V <sub>CCH_GXB[L,R]</sub> | Transceiver high voltage power supply |                                          | 1.710                  | 1.8     | 1.890                  | V    |

#### **Related Information**

- **Transceiver Performance for Arria 10 GT Devices** on page 25 Provides the data rate ranges for different transceiver speed grades.

- Transceiver Performance for Arria 10 GX/SX Devices on page 21 Provides the data rate ranges for different transceiver speed grades.

<sup>&</sup>lt;sup>(11)</sup> These data rate ranges vary depending on the transceiver speed grade. Refer to Transceiver Performance for Arria 10 GT Devices table for exact data rate ranges.

9

### **HPS Power Supply Operating Conditions**

### Table 6: HPS Power Supply Operating Conditions for Arria 10 SX Devices—Preliminary

This table lists the steady-state voltage and current values expected from Arria 10 system-on-a-chip (SoC) devices with ARM®-based hard processor system (HPS). Power supply ramps must all be strictly monotonic, without plateaus. Refer to Recommended Operating Conditions for Arria 10 Devices table for the steady-state voltage values expected from the FPGA portion of the Arria 10 SoC devices.

| Symbol                   | Description                                   | Condition                                        | Minimum <sup>(13)</sup> | Typical | Maximum <sup>(13)</sup> | Unit |

|--------------------------|-----------------------------------------------|--------------------------------------------------|-------------------------|---------|-------------------------|------|

| V <sub>CCL HPS</sub>     | HPS core voltage and periphery                | HPS processor speed = 1.2 GHz                    | 0.87                    | 0.9     | 0.93                    | V    |

| V CCL_HPS                | circuitry power supply                        | HPS processor speed =<br>1.5 GHz, –1 speed grade | 0.92                    | 0.95    | 0.98                    | V    |

|                          |                                               | 3.0 V                                            | 2.85                    | 3.0     | 3.15                    | V    |

| V <sub>CCIO_HPS</sub>    | HPS I/O buffers power supply                  | 2.5 V                                            | 2.375                   | 2.5     | 2.625                   | V    |

|                          |                                               | 1.8 V                                            | 1.71                    | 1.8     | 1.89                    | V    |

| V <sub>CCIOREF_HPS</sub> | HPS I/O pre-driver power supply               | —                                                | 1.71                    | 1.8     | 1.89                    | V    |

| V <sub>CCPLL_HPS</sub>   | HPS PLL analog voltage regulator power supply | _                                                | 1.71                    | 1.8     | 1.89                    | V    |

#### **Related Information**

#### **Recommended Operating Conditions** on page 4

Provides the steady-state voltage values for the FPGA portion of the device.

## **DC** Characteristics

The OCT variation after power-up calibration specifications will be available in a future release of the Arria 10 Device Datasheet.

#### **Supply Current and Power Consumption**

Altera offers two ways to estimate power for your design-the Excel-based Early Power Estimator (EPE) and the Quartus II PowerPlay Power Analyzer feature.

Arria 10 Device Datasheet

<sup>&</sup>lt;sup>(13)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

#### I/O Pin Leakage Current

10

Use the Excel-based EPE before you start your design to estimate the supply current for your design. The EPE provides a magnitude estimate of the device power because these currents vary greatly with the usage of the resources.

The Quartus II PowerPlay Power Analyzer provides better quality estimates based on the specifics of the design after you complete place-androute. The PowerPlay Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, when combined with detailed circuit models, yield very accurate power estimates.

#### **Related Information**

- PowerPlay Early Power Estimator User Guide Provides more information about power estimation tools.

- PowerPlay Power Analysis chapter, Quartus II Handbook Provides more information about power estimation tools.

#### I/O Pin Leakage Current

#### Table 7: I/O Pin Leakage Current for Arria 10 Devices—Preliminary

#### If $V_O = V_{CCIO}$ to $V_{CCIOMAX}$ , 300 µA of leakage current per I/O is expected.

| Symbol          | Description        | Condition                      | Min | Max | Unit |

|-----------------|--------------------|--------------------------------|-----|-----|------|

| II              | Input pin          | $V_I = 0 V$ to $V_{CCIOMAX}$   | -80 | 80  | μΑ   |

| I <sub>OZ</sub> | Tri-stated I/O pin | $V_{O} = 0 V$ to $V_{CCIOMAX}$ | -80 | 80  | μΑ   |

## **Bus Hold Specifications**

The bus-hold trip points are based on calculated input voltages from the JEDEC standard.

## Table 8: Bus Hold Parameters for Arria 10 Devices—Preliminary

|                                             |                   |                                                             |                                           | V <sub>CCIO</sub> (V) |                                            |      |                                              |      |      |      |     |      |      |

|---------------------------------------------|-------------------|-------------------------------------------------------------|-------------------------------------------|-----------------------|--------------------------------------------|------|----------------------------------------------|------|------|------|-----|------|------|

| Parameter                                   | Symbol            | Condition                                                   | 1.                                        | .2                    | 1.                                         | .5   | 1.                                           | .8   | 2.   | .5   | 3   | .0   | Unit |

|                                             |                   |                                                             | Min                                       | Max                   | Min                                        | Max  | Min                                          | Max  | Min  | Max  | Min | Max  |      |

| Bus-hold,<br>low,<br>sustaining<br>current  | I <sub>SUSL</sub> | V <sub>IN</sub> > V <sub>IL</sub><br>(max)                  | 8 <sup>(14)</sup> ,<br>26 <sup>(15)</sup> |                       | 12 <sup>(14)</sup> ,<br>32 <sup>(15)</sup> |      | 30 <sup>(14)</sup> ,<br>55 <sup>(15)</sup>   |      | 60   |      | 70  |      | μΑ   |

| Bus-hold,<br>high,<br>sustaining<br>current | I <sub>SUSH</sub> | V <sub>IN</sub> < V <sub>IH</sub><br>(min)                  | $-8^{(14)},$<br>$-26^{(15)}$              |                       | $-12^{(14)},$<br>$-32^{(15)}$              |      | -30 <sup>(14)</sup> ,<br>-55 <sup>(15)</sup> |      | -60  |      | -70 |      | μΑ   |

| Bus-hold,<br>low,<br>overdrive<br>current   | I <sub>ODL</sub>  | $\begin{array}{c} 0 \ V < V_{IN} \\ < V_{CCIO} \end{array}$ |                                           | 125                   |                                            | 175  |                                              | 200  |      | 300  |     | 500  | μΑ   |

| Bus-hold,<br>high,<br>overdrive<br>current  | I <sub>ODH</sub>  | $\begin{array}{c} 0 \ V < V_{IN} \\ < V_{CCIO} \end{array}$ |                                           | -125                  |                                            | -175 |                                              | -200 |      | -300 |     | -500 | μΑ   |

| Bus-hold<br>trip point                      | V <sub>TRIP</sub> | _                                                           | 0.3                                       | 0.9                   | 0.38                                       | 1.13 | 0.68                                         | 1.07 | 0.70 | 1.7  | 0.8 | 2    | V    |

## **OCT Calibration Accuracy Specifications**

If you enable on-chip termination (OCT) calibration, calibration is automatically performed at power up for I/Os connected to the calibration block.

Arria 10 Device Datasheet

**Altera Corporation**

<sup>&</sup>lt;sup>(14)</sup> This value is only applicable for LVDS I/O bank.

<sup>(15)</sup> This value is only applicable for 3 V I/O bank.

#### 12 **OCT Calibration Accuracy Specifications**

## Table 9: OCT Calibration Accuracy Specifications for Arria 10 Devices—Preliminary

| Calibration accuracy for the calibrated on-chip series termination (R <sub>S</sub> OCT) and on-chip parallel termination (R <sub>T</sub> OCT) are applicable at the moment of |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| calibration. When process, voltage, and temperature (PVT) conditions change after calibration, the tolerance may change.                                                      |

| Symbol                                                                          | Description                                                                                                                                                           | Condition (V)                                  | Ca         | libration Accura | асу        | Unit |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------|------------------|------------|------|

| Symbol                                                                          | Description                                                                                                                                                           | Condition (v)                                  | –E1, –I1   | –E2, –I2         | –E3, –I3   | Onit |

| 48-Ω, 60-Ω, 80-Ω, and 240-Ω $\rm R_S$                                           | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , 80- $\Omega$ , and 240- $\Omega$ setting)                                                 | $V_{CCIO} = 1.2$                               | ±15        | ±15              | ±15        | %    |

| 34- $\Omega$ and 40- $\Omega$ $R_S$                                             | Internal series termination with calibration (34- $\Omega$ and 40- $\Omega$ setting)                                                                                  | V <sub>CCIO</sub> = 1.5, 1.35, 1.25,<br>1.2    | ±15        | ±15              | ±15        | %    |

| 25-Ω R <sub>S</sub>                                                             | Internal series termination with calibration                                                                                                                          | V <sub>CCIO</sub> = 1.8, 1.5, 1.2              | ±15        | ±15              | ±15        | %    |

| 50-Ω R <sub>S</sub>                                                             | Internal series termination with calibration                                                                                                                          | V <sub>CCIO</sub> = 1.8, 1.5, 1.2              | ±15        | ±15              | ±15        | %    |

| 34- $\Omega$ , 40- $\Omega$ , 48- $\Omega$ ,<br>and 60- $\Omega$ R <sub>S</sub> | Internal series termination with calibration (34- $\Omega$ , 40- $\Omega$ , 48- $\Omega$ , and 60- $\Omega$ setting)                                                  | POD12 I/O standard,<br>V <sub>CCIO</sub> = 1.2 | ±15        | ±15              | ±15        | %    |

| 34-Ω, 40-Ω, 48-Ω,<br>60-Ω, 80-Ω, 120-Ω,<br>and 240-Ω R <sub>T</sub>             | Internal parallel termination with calibration (34- $\Omega$ , 40- $\Omega$ , 48- $\Omega$ , 60- $\Omega$ , 80- $\Omega$ , 120- $\Omega$ , and 240- $\Omega$ setting) | POD12 I/O standard,<br>V <sub>CCIO</sub> = 1.2 | ±15        | ±15              | ±15        | %    |

| 60- $\Omega$ and 120- $\Omega$ $R_T$                                            | Internal parallel termination with calibration (60- $\Omega$ and 120- $\Omega$ setting)                                                                               | V <sub>CCIO</sub> = 1.5, 1.35, 1.25, 1.2       | -10 to +40 | -10 to +40       | -10 to +40 | %    |

| 20- $\Omega$ , 30- $\Omega$ , and 40- $\Omega$ $R_{\rm T}$                      | Internal parallel termination with calibration (20- $\Omega$ , 30- $\Omega$ , and 40- $\Omega$ setting)                                                               | V <sub>CCIO</sub> = 1.5, 1.35, 1.25            | -10 to +40 | -10 to +40       | -10 to +40 | %    |

| 50-Ω R <sub>T</sub>                                                             | Internal parallel termination with calibration (50- $\Omega$ setting)                                                                                                 | V <sub>CCIO</sub> = 1.8, 1.5, 1.2              | -10 to +40 | -10 to +40       | -10 to +40 | %    |

#### **OCT Without Calibration Resistance Tolerance Specifications**

#### Table 10: OCT Without Calibration Resistance Tolerance Specifications for Arria 10 Devices—Preliminary

| Symbol               | Description                                                      | Condition (V)                | Re       | Unit     |          |     |

|----------------------|------------------------------------------------------------------|------------------------------|----------|----------|----------|-----|

| Symbol               | Description                                                      |                              | –E1, –I1 | –E2, –I2 | –E3, –I3 | Ont |

| 25-Ω R <sub>S</sub>  | Internal series termination without                              | V <sub>CCIO</sub> = 1.8, 1.5 | ±25      | ±35      | ±40      | %   |

|                      | calibration<br>(25-Ω setting)                                    | $V_{CCIO} = 1.2$             | ±25      | ±35      | ±40      | %   |

|                      | Internal series termination without                              | V <sub>CCIO</sub> = 1.8, 1.5 | ±25      | ±35      | ±40      | %   |

| 50-Ω R <sub>S</sub>  | calibration<br>(50-Ω setting)                                    | $V_{CCIO} = 1.2$             | ±25      | ±35      | ±40      | %   |

| 100-Ω R <sub>D</sub> | Internal differential termination $(100-\Omega \text{ setting})$ | V <sub>CCIO</sub> = 1.8      | ±25      | ±35      | ±40      | %   |

This table lists the Arria 10 OCT without calibration resistance tolerance to PVT changes.

Figure 1: Equation for OCT Variation Without Recalibration—Preliminary

$$R_{OCT} = R_{SCAL} \left( 1 + \left| \frac{dR}{dT} \times \Delta T \right| \pm \left| \frac{dR}{dV} \times \Delta V \right| \right)$$

The definitions for the equation are as follows:

- The R<sub>OCT</sub> value calculated shows the range of OCT resistance with the variation of temperature and V<sub>CCIO</sub>.

- R<sub>SCAL</sub> is the OCT resistance value at power-up.

- $\Delta T$  is the variation of temperature with respect to the temperature at power up.

- $\Delta V$  is the variation of voltage with respect to the V<sub>CCIO</sub> at power up.

- dR/dT is the percentage change of R<sub>SCAL</sub> with temperature.

- dR/dV is the percentage change of  $R_{SCAL}$  with voltage.

### Pin Capacitance

## Table 11: Pin Capacitance for Arria 10 Devices—Preliminary

| Symbol                 | Description                                                  | Value | Unit |

|------------------------|--------------------------------------------------------------|-------|------|

| C <sub>IO_COLUMN</sub> | Input capacitance on column I/O pins                         | 2.5   | pF   |

| C <sub>OUTFB</sub>     | Input capacitance on dual-purpose clock output/feedback pins | 2.5   | pF   |

#### Internal Weak Pull-Up Resistor

All I/O pins, except configuration, test, and JTAG pins, have an option to enable weak pull-up.

### Table 12: Internal Weak Pull-Up Resistor Values for Arria 10 Devices—Preliminary

| Symbol   | Description                                                 | Condition (V) <sup>(16)</sup> | Value <sup>(17)</sup> | Unit |

|----------|-------------------------------------------------------------|-------------------------------|-----------------------|------|

|          |                                                             | $V_{CCIO} = 3.0 \pm 5\%$      | 25                    | kΩ   |

|          |                                                             | $V_{CCIO} = 2.5 \pm 5\%$      | 25                    | kΩ   |

|          | Value of the I/O pin pull-up resistor before and during     | $V_{CCIO} = 1.8 \pm 5\%$      | 25                    | kΩ   |

| $R_{PU}$ | configuration, as well as user mode if you have enabled the | $V_{CCIO} = 1.5 \pm 5\%$      | 25                    | kΩ   |

|          | programmable pull-up resistor option.                       | $V_{CCIO} = 1.35 \pm 5\%$     | 25                    | kΩ   |

|          |                                                             | $V_{CCIO} = 1.25 \pm 5\%$     | 25                    | kΩ   |

|          |                                                             | $V_{CCIO} = 1.2 \pm 5\%$      | 25                    | kΩ   |

#### **Related Information**

### Arria 10 Device Family Pin Connection Guidelines

Provides more information about the pins that support internal weak pull-up and internal weak pull-down features.

$<sup>^{(16)}</sup>$  Pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{CCIO}$ .

$<sup>^{(17)}</sup>$  Valid with ±10% tolerances to cover changes over PVT.

#### I/O Standard Specifications 15

## I/O Standard Specifications

Tables in this section list the input voltage ( $V_{IH}$  and  $V_{IL}$ ), output voltage ( $V_{OH}$  and  $V_{OL}$ ), and current drive characteristics ( $I_{OH}$  and  $I_{OL}$ ) for various I/O standards supported by Arria 10 devices.

For minimum voltage values, use the minimum V<sub>CCIO</sub> values. For maximum voltage values, use the maximum V<sub>CCIO</sub> values.

You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.

#### **Related Information**

**Recommended Operating Conditions** on page 4

#### Single-Ended I/O Standards Specifications

## Table 13: Single-Ended I/O Standards Specifications for Arria 10 Devices—Preliminary

| I/O Standard    |       | V <sub>CCIO</sub> (V) |         |      | V <sub>IL</sub> (V)    | V <sub>IH</sub>        | (V)              | V <sub>OL</sub> (V) V <sub>OH</sub> (V) |                          | I <sub>OL</sub> <sup>(18)</sup> | I <sub>OH</sub> <sup>(18)</sup> (mA) |

|-----------------|-------|-----------------------|---------|------|------------------------|------------------------|------------------|-----------------------------------------|--------------------------|---------------------------------|--------------------------------------|

|                 | Min   | Тур                   | Тур Мах |      | Мах                    | Min Max                |                  | Мах                                     | Min                      | (mA)                            | IOH ( (IIIA)                         |

| 3.0-V<br>LVTTL  | 2.85  | 3                     | 3.15    | -0.3 | 0.8                    | 1.7                    | 3.3              | 0.4                                     | 2.4                      | 2                               | -2                                   |

| 3.0-V<br>LVCMOS | 2.85  | 3                     | 3.15    | -0.3 | 0.8                    | 1.7                    | 3.3              | 0.2                                     | V <sub>CCIO</sub> – 0.2  | 0.1                             | -0.1                                 |

| 2.5 V           | 2.375 | 2.5                   | 2.625   | -0.3 | 0.7                    | 1.7                    | 3.3              | 0.4                                     | 2                        | 1                               | -1                                   |

| 1.8 V           | 1.71  | 1.8                   | 1.89    | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{CCIO} + 0.3$ | 0.45                                    | V <sub>CCIO</sub> – 0.45 | 2                               | -2                                   |

| 1.5 V           | 1.425 | 1.5                   | 1.575   | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{CCIO} + 0.3$ | $0.25 \times V_{CCIO}$                  | $0.75 \times V_{CCIO}$   | 2                               | -2                                   |

| 1.2 V           | 1.14  | 1.2                   | 1.26    | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{CCIO} + 0.3$ | $0.25 \times V_{CCIO}$                  | $0.75 \times V_{CCIO}$   | 2                               | -2                                   |

<sup>&</sup>lt;sup>(18)</sup> To meet the I<sub>OL</sub> and I<sub>OH</sub> specifications, you must set the current strength settings accordingly. For example, to meet the 3.0-V LVTTL specification (2 mA), you should set the current strength settings to 2 mA. Setting at lower current strength may not meet the IOI and IOH specifications in the datasheet.

#### Single-Ended SSTL, HSTL, and HSUL I/O Reference Voltage Specifications

#### Table 14: Single-Ended SSTL, HSTL, and HSUL I/O Reference Voltage Specifications for Arria 10 Devices—Preliminary

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       |                        | V <sub>REF</sub> (V)  |                        | V <sub>TT</sub> (V)    |                       |                        |  |  |

|------------------------|-------|-----------------------|-------|------------------------|-----------------------|------------------------|------------------------|-----------------------|------------------------|--|--|

| I/O Standard           | Min   | Тур                   | Мах   | Min                    | Тур                   | Мах                    | Min                    | Тур                   | Max                    |  |  |

| SSTL-18<br>Class I, II | 1.71  | 1.8                   | 1.89  | 0.833                  | 0.9                   | 0.969                  | $V_{REF} - 0.04$       | V <sub>REF</sub>      | $V_{REF} + 0.04$       |  |  |

| SSTL-15<br>Class I, II | 1.425 | 1.5                   | 1.575 | $0.49 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ | $0.49 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ |  |  |

| SSTL-135               | 1.283 | 1.35                  | 1.418 | $0.49 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ | $0.49 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ |  |  |

| SSTL-125               | 1.19  | 1.25                  | 1.31  | $0.49 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ | $0.49 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ |  |  |

| SSTL-12                | 1.14  | 1.2                   | 1.26  | $0.49 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ | $0.49 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ |  |  |

| HSTL-18<br>Class I, II | 1.71  | 1.8                   | 1.89  | 0.85                   | 0.9                   | 0.95                   |                        | $V_{CCIO}/2$          | _                      |  |  |

| HSTL-15<br>Class I, II | 1.425 | 1.5                   | 1.575 | 0.68                   | 0.75                  | 0.9                    |                        | $V_{\rm CCIO}/2$      | _                      |  |  |

| HSTL-12<br>Class I, II | 1.14  | 1.2                   | 1.26  | $0.47 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$ | $0.53 \times V_{CCIO}$ | _                      | V <sub>CCIO</sub> /2  | _                      |  |  |

| HSUL-12                | 1.14  | 1.2                   | 1.3   | $0.49 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ |                        |                       | _                      |  |  |

| POD12                  | 1.16  | 1.2                   | 1.24  | $0.69 \times V_{CCIO}$ | $0.7 \times V_{CCIO}$ | $0.71 \times V_{CCIO}$ |                        | V <sub>CCIO</sub>     |                        |  |  |

## Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications

| I/O Standard        | ١     | / <sub>IL(DC)</sub> (V) | V <sub>IH(D</sub>        | <sub>C)</sub> (V)        | V <sub>IL(AC)</sub> (V)  | V <sub>IH(AC)</sub> (V)  | V <sub>OL</sub> (V)     | V <sub>OH</sub> (V)     | I <sub>OL</sub> <sup>(19)</sup> | I <sub>OH</sub> <sup>(19)</sup> |

|---------------------|-------|-------------------------|--------------------------|--------------------------|--------------------------|--------------------------|-------------------------|-------------------------|---------------------------------|---------------------------------|

| I/O Stanuaru        | Min   | Мах                     | Min                      | Мах                      | Мах                      | Min                      | Мах                     | Min                     | (mA)                            | (mA)                            |

| SSTL-18<br>Class I  | -0.3  | V <sub>REF</sub> -0.125 | V <sub>REF</sub> + 0.125 | $V_{CCIO} + 0.3$         | V <sub>REF</sub> – 0.25  | V <sub>REF</sub> + 0.25  | V <sub>TT</sub> – 0.603 | V <sub>TT</sub> + 0.603 | 6.7                             | -6.7                            |

| SSTL-18<br>Class II | -0.3  | V <sub>REF</sub> -0.125 | V <sub>REF</sub> + 0.125 | $V_{CCIO} + 0.3$         | V <sub>REF</sub> – 0.25  | V <sub>REF</sub> + 0.25  | 0.28                    | V <sub>CCIO</sub> –0.28 | 13.4                            | -13.4                           |

| SSTL-15<br>Class I  | _     | V <sub>REF</sub> – 0.1  | $V_{REF} + 0.1$          |                          | V <sub>REF</sub> – 0.175 | V <sub>REF</sub> + 0.175 | $0.2 \times V_{CCIO}$   | $0.8 \times V_{CCIO}$   | 8                               | -8                              |

| SSTL-15<br>Class II | _     | V <sub>REF</sub> – 0.1  | $V_{REF} + 0.1$          |                          | V <sub>REF</sub> – 0.175 | V <sub>REF</sub> + 0.175 | $0.2 \times V_{CCIO}$   | $0.8 \times V_{CCIO}$   | 16                              | -16                             |

| SSTL-135            | _     | V <sub>REF</sub> – 0.09 | V <sub>REF</sub> + 0.09  |                          | V <sub>REF</sub> – 0.16  | V <sub>REF</sub> + 0.16  | $0.2 \times V_{CCIO}$   | $0.8 \times V_{CCIO}$   | —                               | _                               |

| SSTL-125            |       | $V_{REF}$ – 0.09        | $V_{REF} + 0.09$         |                          | V <sub>REF</sub> – 0.15  | $V_{REF} + 0.15$         | $0.2 \times V_{CCIO}$   | $0.8 \times V_{CCIO}$   | —                               | —                               |

| SSTL-12             |       | V <sub>REF</sub> – 0.10 | $V_{REF} + 0.10$         |                          | V <sub>REF</sub> – 0.15  | $V_{REF} + 0.15$         | $0.2 \times V_{CCIO}$   | $0.8 \times V_{CCIO}$   | —                               | _                               |

| HSTL-18<br>Class I  | _     | $V_{REF}$ –0.1          | $V_{REF} + 0.1$          |                          | V <sub>REF</sub> – 0.2   | $V_{REF} + 0.2$          | 0.4                     | $V_{CCIO} - 0.4$        | 8                               | -8                              |

| HSTL-18<br>Class II |       | V <sub>REF</sub> – 0.1  | $V_{REF} + 0.1$          |                          | V <sub>REF</sub> – 0.2   | $V_{REF} + 0.2$          | 0.4                     | $V_{CCIO} - 0.4$        | 16                              | -16                             |

| HSTL-15<br>Class I  | _     | V <sub>REF</sub> – 0.1  | $V_{REF} + 0.1$          |                          | V <sub>REF</sub> – 0.2   | $V_{REF} + 0.2$          | 0.4                     | $V_{CCIO} - 0.4$        | 8                               | -8                              |

| HSTL-15<br>Class II |       | V <sub>REF</sub> – 0.1  | $V_{REF} + 0.1$          |                          | V <sub>REF</sub> – 0.2   | $V_{REF} + 0.2$          | 0.4                     | V <sub>CCIO</sub> -0.4  | 16                              | -16                             |

| HSTL-12<br>Class I  | -0.15 | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08  | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | $0.25 \times V_{CCIO}$  | $0.75 \times V_{CCIO}$  | 8                               | -8                              |

<sup>&</sup>lt;sup>(19)</sup> To meet the I<sub>OL</sub> and I<sub>OH</sub> specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the I<sub>OL</sub> and I<sub>OH</sub> specifications in the datasheet.

| I/O Standard –      | ١     | V <sub>IL(DC)</sub> (V) | V <sub>IH(D</sub>       | <sub>C)</sub> (V)        | V <sub>IL(AC)</sub> (V) | V <sub>IH(AC)</sub> (V) | V <sub>OL</sub> (V)                                            | V <sub>OH</sub> (V)                                            | I <sub>OL</sub> <sup>(19)</sup> | I <sub>OH</sub> <sup>(19)</sup> |

|---------------------|-------|-------------------------|-------------------------|--------------------------|-------------------------|-------------------------|----------------------------------------------------------------|----------------------------------------------------------------|---------------------------------|---------------------------------|

|                     | Min   | Мах                     | Min Max                 |                          | Max                     | Min                     | Мах                                                            | Min                                                            | (mA)                            | (mA)                            |

| HSTL-12<br>Class II | -0.15 | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> – 0.15 | V <sub>REF</sub> + 0.15 | $0.25 \times V_{CCIO}$                                         | $0.75 \times V_{CCIO}$                                         | 16                              | -16                             |

| HSUL-12             | _     | V <sub>REF</sub> - 0.13 | $V_{REF} + 0.13$        | _                        | V <sub>REF</sub> – 0.22 | $V_{REF} + 0.22$        | $0.1 \times V_{CCIO}$                                          | $0.9 \times V_{CCIO}$                                          |                                 | —                               |

| POD12               | -0.15 | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> – 0.15 | V <sub>REF</sub> + 0.15 | $\begin{array}{c} (0.7-0.15)\times\\ V_{\rm CCIO} \end{array}$ | $\begin{array}{c} (0.7+0.15)\times\\ V_{\rm CCIO} \end{array}$ |                                 | _                               |

Differential SSTL I/O Standards Specifications

## Table 16: Differential SSTL I/O Standards Specifications for Arria 10 Devices—Preliminary

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       | V <sub>SWING(DC)</sub> (V) |                  | V <sub>SWING</sub>                            | <sub>(AC)</sub> (V)                           | V <sub>IX(AC)</sub> (V)         |                      |                             |  |  |

|------------------------|-------|-----------------------|-------|----------------------------|------------------|-----------------------------------------------|-----------------------------------------------|---------------------------------|----------------------|-----------------------------|--|--|

|                        | Min   | Тур                   | Max   | Min                        | Мах              | Min                                           | Мах                                           | Min                             | Тур                  | Мах                         |  |  |

| SSTL-18<br>Class I, II | 1.71  | 1.8                   | 1.89  | 0.25                       | $V_{CCIO} + 0.6$ | 0.5                                           | $V_{CCIO} + 0.6$                              | V <sub>CCIO</sub> /2 –<br>0.175 | _                    | $V_{\rm CCIO}/2 + 0.175$    |  |  |

| SSTL-15<br>Class I, II | 1.425 | 1.5                   | 1.575 | 0.2                        | (20)             | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | 2(V <sub>REF</sub> –<br>V <sub>IL(AC)</sub> ) | V <sub>CCIO</sub> /2 –<br>0.15  | _                    | V <sub>CCIO</sub> /2 + 0.15 |  |  |

| SSTL-135               | 1.283 | 1.35                  | 1.45  | 0.18                       | (20)             | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | 2(V <sub>IL(AC)</sub> –<br>V <sub>REF</sub> ) | V <sub>CCIO</sub> /2 –<br>0.15  | V <sub>CCIO</sub> /2 | $V_{\rm CCIO}/2 + 0.15$     |  |  |

| SSTL-125               | 1.19  | 1.25                  | 1.31  | 0.18                       | (20)             | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | 2(V <sub>IL(AC)</sub> –<br>V <sub>REF</sub> ) | V <sub>CCIO</sub> /2 –<br>0.15  | V <sub>CCIO</sub> /2 | $V_{CCIO}/2 + 0.15$         |  |  |

| SSTL-12                | 1.14  | 1.2                   | 1.26  | 0.16                       | (20)             | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | 2(V <sub>IL(AC)</sub> –<br>V <sub>REF</sub> ) | V <sub>REF</sub> – 0.15         | V <sub>CCIO</sub> /2 | V <sub>REF</sub> + 0.15     |  |  |

| POD12                  | 1.16  | 1.2                   | 1.24  | 0.16                       | —                | 0.3                                           | _                                             | V <sub>REF</sub> - 0.08         | —                    | V <sub>REF</sub> + 0.08     |  |  |

<sup>(19)</sup> To meet the I<sub>OL</sub> and I<sub>OH</sub> specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the I<sub>OL</sub> and I<sub>OH</sub> specifications in the datasheet.

$^{(20)}$  The maximum value for  $V_{SWING(DC)}$  is not defined. However, each single-ended signal needs to be within the respective single-ended limits ( $V_{IH(DC)}$  and  $V_{IL(DC)}$ ).

#### Differential HSTL and HSUL I/O Standards Specifications

| I/O Standard           | V <sub>CCIO</sub> (V) |     | V <sub>DIF(DC)</sub> (V) |                                               | V <sub>DIF(AC)</sub> (V)                      |                                               | V <sub>IX(AC)</sub> (V)                       |                                                                     |                            | V <sub>CM(DC)</sub> (V)      |                          |                          |                           |

|------------------------|-----------------------|-----|--------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------|----------------------------|------------------------------|--------------------------|--------------------------|---------------------------|

|                        | Min                   | Тур | Max                      | Min                                           | Max                                           | Min                                           | Max                                           | Min                                                                 | Тур                        | Max                          | Min                      | Тур                      | Max                       |

| HSTL-18<br>Class I, II | 1.71                  | 1.8 | 1.89                     | 0.2                                           | _                                             | 0.4                                           |                                               | 0.78                                                                | _                          | 1.12                         | 0.78                     | _                        | 1.12                      |

| HSTL-15<br>Class I, II | 1.425                 | 1.5 | 1.575                    | 0.2                                           | _                                             | 0.4                                           | _                                             | 0.68                                                                | _                          | 0.9                          | 0.68                     | _                        | 0.9                       |

| HSTL-12<br>Class I, II | 1.14                  | 1.2 | 1.26                     | 0.16                                          | $V_{CCIO} + 0.3$                              | 0.3                                           | $V_{CCIO} + 0.48$                             | _                                                                   | $0.5 \times V_{ m CCIO}$   | —                            | $0.4 \times V_{ m CCIO}$ | $0.5 \times V_{ m CCIO}$ | $0.6 \times V_{\rm CCIO}$ |

| HSUL-12                | 1.14                  | 1.2 | 1.3                      | 2(V <sub>IH(DC)</sub><br>– V <sub>REF</sub> ) | 2(V <sub>REF</sub> –<br>V <sub>IH(DC)</sub> ) | 2(V <sub>IH(AC)</sub><br>– V <sub>REF</sub> ) | 2(V <sub>REF</sub> –<br>V <sub>IH(AC)</sub> ) | $\begin{array}{c} 0.5 \times \\ V_{\rm CCIO} - \\ 0.12 \end{array}$ | 0.5 ×<br>V <sub>CCIO</sub> | $0.5 \times V_{CCIO} + 0.12$ | $0.4 \times V_{CCIO}$    | $0.5 \times V_{CCIO}$    | $0.6 \times V_{CCIO}$     |

## Table 17: Differential HSTL and HSUL I/O Standards Specifications for Arria 10 Devices—Preliminary

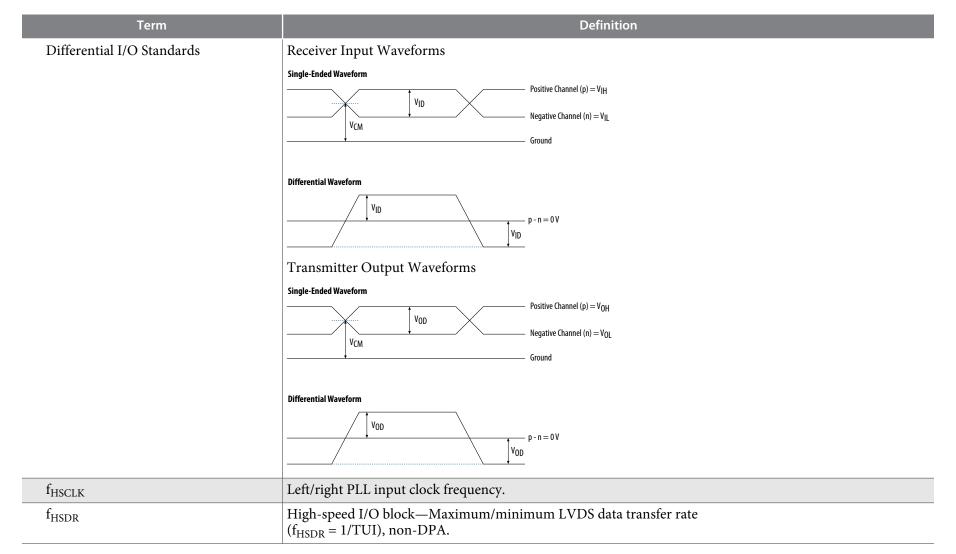

## **Differential I/O Standards Specifications**

## Table 18: Differential I/O Standards Specifications for Arria 10 Devices—Preliminary

Differential inputs are powered by V<sub>CCPT</sub> which requires 1.8 V.

| I/O Standard - |        | V <sub>CCIO</sub> (V)                                                                                                                                                                                                                                            |     |     | V <sub>ID</sub> (mV) <sup>(21)</sup> |     |     | V <sub>ICM(DC)</sub> (V) |     |     | V <sub>OD</sub> (V) <sup>(22)</sup> |     |     | V <sub>OCM</sub> (V) <sup>(22)</sup> |     |  |

|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------------------|-----|-----|--------------------------|-----|-----|-------------------------------------|-----|-----|--------------------------------------|-----|--|

|                | Min    | Тур                                                                                                                                                                                                                                                              | Max | Min | Condition                            | Max | Min | Condition                | Max | Min | Тур                                 | Max | Min | Тур                                  | Max |  |

| PCML           | Transn | Transmitter, receiver, and input reference clock pins of high-speed transceivers use the CML I/O standard. For transmitter, receiver, and reference clock I/O pin specifications, refer to Transceiver Specifications for Arria 10 GX, SX, and GT Devices table. |     |     |                                      |     |     |                          |     |     |                                     |     |     |                                      |     |  |

(22)  $R_{\rm L}$  range:  $90 \le R_{\rm L} \le 110 \ \Omega$ .

Arria 10 Device Datasheet

$<sup>^{(21)}</sup>$  The minimum V<sub>ID</sub> value is applicable over the entire common mode range, V<sub>CM</sub>.

| I/O Standard                       |                                             |     | V <sub>ID</sub> (mV) <sup>(21)</sup> |      |                             | V <sub>ICM(DC)</sub> (V) |     | V <sub>OD</sub> (V) <sup>(22)</sup> |       | 2)    | V <sub>OCM</sub> (V) <sup>(22)</sup> |     |       |      |       |

|------------------------------------|---------------------------------------------|-----|--------------------------------------|------|-----------------------------|--------------------------|-----|-------------------------------------|-------|-------|--------------------------------------|-----|-------|------|-------|

| 1/O Standard                       | Min                                         | Тур | Мах                                  | Min  | Condition                   | Max                      | Min | Condition                           | Max   | Min   | Тур                                  | Max | Min   | Тур  | Max   |

| LVDS <sup>(23)</sup>               | $VDS^{(23)}$ 1.71 1.8 1.89 100 $V_{CM} = -$ | 0   | D <sub>MAX</sub><br>≤700 Mbps        | 1.85 | 0.247                       |                          | 0.6 | 1.125                               | 1.25  | 1.375 |                                      |     |       |      |       |

|                                    | 1.71                                        | 1.0 | 1.09                                 | 100  | 1.25 V                      |                          | 1   | D <sub>MAX</sub> ><br>700 Mbps      | 1.6   | 0.247 |                                      | 0.0 | 1.123 | 1.25 | 1.373 |

| RSDS (HIO)<br>(24)                 | 1.71                                        | 1.8 | 1.89                                 | 100  | V <sub>CM</sub> =<br>1.25 V | —                        | 0.3 | _                                   | 1.4   | 0.1   | 0.2                                  | 0.6 | 0.5   | 1.2  | 1.4   |

| Mini-LVDS<br>(HIO) <sup>(25)</sup> | 1.71                                        | 1.8 | 1.89                                 | 200  | _                           | 600                      | 0.4 | _                                   | 1.325 | 0.25  |                                      | 600 | 1     | 1.2  | 1.4   |

| LVPECL <sup>(26)</sup>             | 1.71                                        | 1.8 | 1.89                                 | 300  |                             |                          | 0.6 | D <sub>MAX</sub><br>≤700 Mbps       | 1.7   |       |                                      |     |       |      |       |

| LVIECL                             | 1./1                                        | 1.0 | 1.09                                 | 500  |                             |                          | 1   | D <sub>MAX</sub> ><br>700 Mbps      | 1.6   |       |                                      |     |       |      |       |

#### **Related Information**

Transceiver Specifications for Arria 10 GX, SX, and GT Devices on page 28

Provides the specifications for transmitter, receiver, and reference clock I/O pin.

# **Switching Characteristics**

This section provides the performance characteristics of Arria 10 core and periphery blocks for extended grade devices.

$<sup>^{(21)}\,</sup>$  The minimum  $V_{ID}$  value is applicable over the entire common mode range,  $V_{CM}.$

<sup>&</sup>lt;sup>(22)</sup>  $R_L$  range:  $90 \le R_L \le 110 \Omega$ .

<sup>&</sup>lt;sup>(23)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be within 1.0 V to 1.6 V for data rates above 700 Mbps and 0 V to 1.85 V for data rates below 700 Mbps.

<sup>&</sup>lt;sup>(24)</sup> For optimized RSDS receiver performance, the receiver voltage input range must be within 0.3 V to 1.4 V.

<sup>&</sup>lt;sup>(25)</sup> For optimized Mini-LVDS receiver performance, the receiver voltage input range must be within 0.4 V to 1.325 V.

<sup>&</sup>lt;sup>(26)</sup> For optimized LVPECL receiver performance, the receiver voltage input range must be within 0.85 V to 1.75 V for data rates above 700 Mbps and 0.45 V to 1.95 V for data rates below 700 Mbps.

# **Transceiver Performance Specifications**

## Transceiver Performance for Arria 10 GX/SX Devices

#### Table 19: Transmitter and Receiver Data Rate Performance—Preliminary

| Symbol/Description           | Condition                                                                   | Transceiver<br>Speed Grade 1 | Transceiver<br>Speed Grade 2 | Transceiver<br>Speed Grade 3 | Transceiver<br>Speed Grade 4 | Transceiver<br>Speed Grade 5<br>(27) | Unit |

|------------------------------|-----------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|--------------------------------------|------|

| Chip-to-Chip <sup>(28)</sup> | Maximum data rate<br>$V_{CCR\_GXB} = V_{CCT\_GXB}$<br>= 1.03 V              | 17.4                         | 15                           | 14.2                         | 12.5                         | 8                                    | Gbps |

|                              | Maximum data rate<br>$V_{CCR\_GXB} = V_{CCT\_GXB}$<br>= 0.9 V               | 11.3                         | 11.3                         | 11.3                         | 11.3                         | 8                                    | Gbps |

|                              | TX Minimum Data<br>Rate                                                     |                              | Mbps                         |                              |                              |                                      |      |

|                              | RX Minimum Data<br>Rate                                                     |                              |                              | 1.0 (29)                     |                              |                                      | Gbps |

| Backplane <sup>(28)</sup>    | Maximum data rate<br>V <sub>CCR_GXB</sub> = V <sub>CCT_GXB</sub><br>= 1.0 V | 16                           | 14.2                         | 12.5                         | 10.3125                      | 6.5536                               | Gbps |

Arria 10 Device Datasheet

<sup>&</sup>lt;sup>(27)</sup> Transceiver speed grade 5 supports PCIe Gen3.

<sup>&</sup>lt;sup>(28)</sup> Backplane applications assume advanced equalization circuitry, such as decision feedback equalization (DFE), is enabled to compensate for signal impairments. Chip-to-chip links are assumed to be applications with short reach channels that do not require DFE.

<sup>&</sup>lt;sup>(29)</sup> Arria 10 transceivers can support data rates down to 125 Mbps with over sampling.

#### 22 Transceiver Performance for Arria 10 GX/SX Devices

| Symbol/Description | Condition                                                     | Transceiver<br>Speed Grade 1 | Transceiver<br>Speed Grade 2 | Transceiver<br>Speed Grade 3 | Transceiver<br>Speed Grade 4 | Transceiver<br>Speed Grade 5<br>(27) | Unit |

|--------------------|---------------------------------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|--------------------------------------|------|

|                    | Maximum data rate<br>$V_{CCR\_GXB} = V_{CCT\_GXB}$<br>= 0.9 V | 10.3125                      | 10.3125                      | 10.3125                      | 10.3125                      | 6.5536                               | Gbps |

|                    | TX Minimum Data<br>Rate                                       |                              | Mbps                         |                              |                              |                                      |      |

|                    | RX Minimum Data<br>Rate                                       |                              |                              | 1.0 (29)                     |                              |                                      | Gbps |

## Table 20: ATX PLL Performance—Preliminary

| Symbol/Descrip-<br>tion          | Condition            | Transceiver<br>Speed Grade 1 | Transceiver<br>Speed Grade 2 | Transceiver<br>Speed Grade 3 | Transceiver<br>Speed Grade 4 | Transceiver<br>Speed Grade 5 | Unit |  |

|----------------------------------|----------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------|--|

| Supported<br>Output<br>Frequency | Maximum<br>Frequency | 8.7 7.5 7.1 6.25 4           |                              |                              |                              |                              | GHz  |  |

|                                  | Minimum<br>Frequency |                              | 305.5                        |                              |                              |                              |      |  |

## Table 21: Fractional PLL Performance—Preliminary

| Symbol/<br>Description | Condition            | Transceiver<br>Speed Grade 1 | Transceiver<br>Speed Grade 2 | Transceiver<br>Speed Grade 3 | Transceiver<br>Speed Grade 4 | Transceiver<br>Speed Grade 5 | Unit |  |  |

|------------------------|----------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------|--|--|

| Supported              | Maximum<br>Frequency | 6.25                         | 6.25                         | 6.25                         | 6.25                         | 4                            | GHz  |  |  |

| Output<br>Frequency    | Minimum<br>Frequency |                              | 305.5                        |                              |                              |                              |      |  |  |

(27) Transceiver speed grade 5 supports PCIe Gen3.

## Table 22: CMU PLL Performance—Preliminary

| Symbol/<br>Description | Condition            | Transceiver<br>Speed Grade 1 | Transceiver<br>Speed Grade 2 | Transceiver<br>Speed Grade 3 | Transceiver<br>Speed Grade 4 | Transceiver<br>Speed Grade 5 | Unit |  |

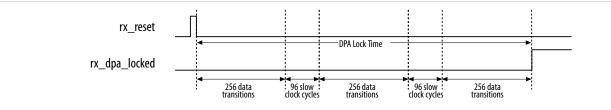

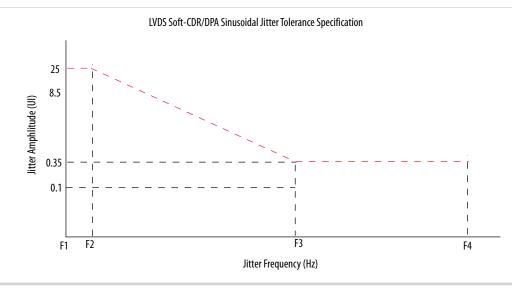

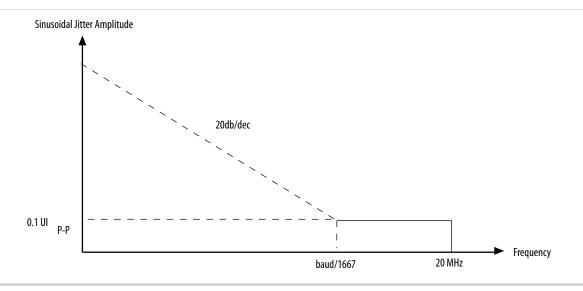

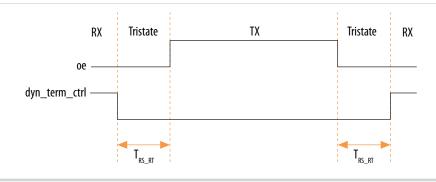

|------------------------|----------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------|--|